- 1. Trois moteurs : le transistor, le circuit intégré et le microprocesseur

- 2. L'essor de la microélectronique

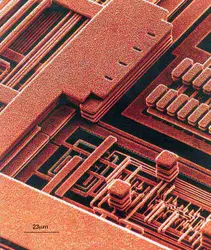

- 3. La fabrication des circuits intégrés

- 4. Les limites physiques aux circuits intégrés

- 5. Les progrès en miniaturisation

- 6. Mémorisation et traitement de l'information en microélectronique

- 7. Microélectronique et performance des ordinateurs

- 8. Les nouveaux effets physiques « quantiques » apparaissant en nanoélectronique

- 9. La microélectronique : quels impacts à venir ?

- 10. Bibliographie

- 11. Internet

MICROÉLECTRONIQUE

Article modifié le

Les limites physiques aux circuits intégrés

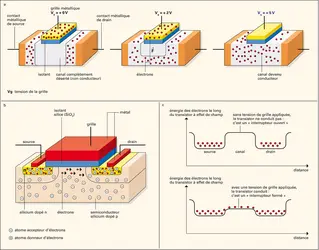

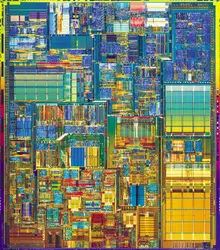

À partir des trois éléments de base des circuits intégrés (transistor, résistance et condensateur), toutes les fonctions requises par « l'intelligence » informatique peuvent être réalisées (fig. 7). Plus les éléments fabriqués seront de petite taille, plus on pourra en intégrer sur une seule puce. L'augmentation de la miniaturisation se traduit donc, depuis le milieu des années 1970, par une puissance de calcul toujours croissante. Quelles sont les limites physiques au bon fonctionnement des éléments et des interconnexions ?

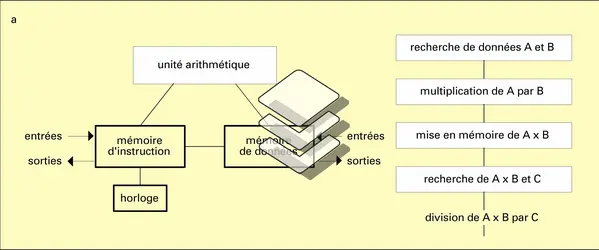

Pour simplifier, les effets physiques de la diminution de taille des éléments des circuits intégrés sont analysés en introduisant un paramètre a de diminution de l'échelle des éléments, qui passent d'un taille 1 à une taille 1/a (fig. 8). Par cette « loi d'échelle », la taille linéaire des éléments décroît de a et leur densité surfacique augmente de a2. On en déduit alors, le fonctionnement du transistor se faisant à champ électrique accélérateur constant entre la source et le drain (donc à vitesse v des électrons constante), que le potentiel électrique de commande du transistor décroît de a. Si cette loi d'échelle était parfaitement respectée (ce qui n'est pas le cas, comme on va le voir plus loin), la vitesse d'un composant – déterminée, en première approximation, par le temps mis par un électron pour passer, sous la grille de longueur LG, de la source au drain, soit LG / v – croîtrait d'un facteur a. Ainsi, pour un circuit intégré de surface donnée, la réduction des dimensions de ces éléments d'un facteur 10 (a = 10), permet d'augmenter sa « puissance logique » (produit du nombre de composants par leur vitesse individuelle) d'un facteur 1 000 (100 pour la densité des transistors et 10 pour leur vitesse). L'intérêt est donc de réduire les dimensions jusqu'aux limites du « bon » fonctionnement du transistor comme « interrupteur parfait » (fig. 9) : cela suppose à la fois qu'il ait une très faible résistance au passage du courant en position « fermée » (tension de grille VG=tension « 1 » logique), qu'il ne conduise pas le courant lorsqu'il est « ouvert » (VG = 0) et que la commande du transistor, considéré comme un interrupteur parfait, ne fuie pas (c'est-à-dire que le courant passant de l'électrode de grille au canal conducteur soit à peu près nul). La première condition ne pose pas de problème sérieux, mais les deux autres créent des difficultés lorsque l'on cherche à atteindre les limites physiques du transistor.

Pour que le transistor ne conduise pas en l'absence de tension appliquée à la grille, les barrières de potentiel existant autour de la source et du drain (fig. 1c) ne doivent pas se rejoindre (sinon, la barrière de potentiel empêchant les électrons de passer d'une région à l'autre serait trop faible). L'extension spatiale des barrières peut être réduite en augmentant les dopages (concentrations) en atomes donneurs ou accepteurs d'électrons, ce qui n'est possible que jusqu'à une concentration limite en impuretés de l'ordre d'une impureté pour dix mille atomes de silicium. Au-delà se posent des problèmes métallurgiques (agglomération des atomes d'impuretés pour former des amas métalliques), d'une part, et de conductivité électrique dégradée, d'autre part. Il apparaît, à cause de cet effet d'extension finie des barrières, une limite à la longueur de la grille, qui est de l'ordre de 50 nm, si l'on arrive à une parfaite maîtrise des dopages dans les géométries classiques des transistors. Pour aller au-delà, de nouvelles géométries de transistors, où les électrons sont beaucoup plus confinés verticalement, sont nécessaires : c'est le cas du transistor à double grille ou du transistor à grille enveloppante (surrounding gate) (fig. 10), dont la mise en œuvre dans les circuits intégrés futurs permettra d'atteindre une longueur de grille de l'ordre de 5 à 10 nm.

Les lois d'échelle imposent aussi à l'épaisseur d'isolant de la grille de décroître d'un facteur a. À partir d'une épaisseur minimale de l'ordre de 4 nm, l'isolant de la grille se met à fuir par l'apparition d'un phénomène quantique, l'effet tunnel, qui permet aux électrons de passer à travers la barrière de potentiel constitué par l'isolant. L'effet tunnel est intimement lié à la nature ondulatoire de l'électron : à l'électron, comme à toute particule, est associée une onde, dite onde de De Broglie, qui régit son comportement sur les courtes distances. Cette onde s'atténue exponentiellement dans un isolant sur une distance de l'ordre de quelques nanomètres. Lorsque l'isolant est épais, l'onde située d'un côté de l'isolant a une amplitude négligeable de l'autre côté, ce qui se traduit par une très faible possibilité pour l'électron de passer de l'autre côté, même si un champ électrique ou une concentration d'électrons moindre l'y attirent. En revanche, cette probabilité de présence de l'électron de l'autre côté de l'isolant croit très vite lorsque l'épaisseur de l'isolant diminue, et le courant tunnel associé devient une fuite insupportable dès que l'épaisseur de silice atteint des valeurs de l'ordre de 2 nm. La puissance consommée par ce courant devient supérieure à celle qui est nécessaire à l'exécution des opérations logiques. La solution à ce problème est de mettre en œuvre des isolants qui auraient une épaisseur supérieure à celle de la silice, correspondant à l'échelle du transistor, tout en remplissant la fonction de contrôle du canal aussi bien qu'une silice d'épaisseur plus faible. Pour cela, on doit utiliser un matériau ayant une constante diélectrique plus élevée que celle de la silice. Ce type de matériau fait l'objet de nombreuses recherches.

Il existe d'autres facteurs limitant la miniaturisation que ces simples limites géométriques liés à la longueur de canal et l'épaisseur de l'isolant de la grille. La première concerne la tension logique (tension définissant les « 0 » et « 1 » logiques, qui est très proche de la tension d'alimentation du circuit) que l'on retrouve approximativement à la fois comme tension de commande de la grille et comme tension accélératrice des électrons entre source et drain. Cette tension logique doit être nettement plus grande que les fluctuations statistiques inévitables des niveaux de tension logiques « 0 » ou « 1 » afin d'éviter les erreurs logiques intempestives. Sans entrer dans le détail, disons simplement qu'une tension logique dix fois plus grande que les fluctuations prévisibles donne un taux d'erreur acceptable. Ces fluctuations sont essentiellement déterminées par l'agitation thermique – qui vaut, à la température ambiante, 25 millivolts (mV) –, par le nombre aléatoire d'impuretés dopantes sous la grille et, surtout, par le désordre technologique. Ce dernier, qui correspond aux différentes valeurs de dopages et de taille des éléments du transistor, donne une fluctuation de la tension de la commande de la transition de transistor d'ouvert à fermé de l'ordre de 100 mV. De ce fait, la tension logique minimale doit être de l'ordre du volt, à moins que l'on ne progresse de manière décisive pour réduire les fluctuations technologiques et contrôler leurs effets, ainsi que celle du bruit thermique, ce qui semble improbable alors que l'on continue à miniaturiser. Cela est une des limitations aux lois d'échelle décrites plus haut. De plus, comme un minimum d'interopérabilité entre les composants électroniques de générations différentes est souhaité, les tensions logiques sont standardisées par un accord international entre fabricants. Celles-ci, qui changent rarement, sont passées de 12 V à 5 V en 1975, puis à 3,3 V en 1989, et 1,5 V depuis 2000. Cette valeur se rapproche nettement de celles qu'imposent les fluctuations thermiques et le désordre technologique.

D'autres problèmes apparaissent quand les dimensions diminuent : le champ électrique (rapport entre la tension logique et la distance entre les électrodes source et drain) devient de plus en plus grand ; les électrons sont alors plus énergétiques et dégradent l'isolant. De nouvelles géométries de dopage, souvent complexes, sont utilisées pour contrôler le profil du champ électrique. Toutefois, grâce à cette augmentation du champ électrique, les électrons sont plus rapides et la fréquence des circuits intégrés progresse plus vite que les simples lois d'échelle.

Une autre limite physique additionnelle, déjà largement atteinte, concerne la puissance dissipée par les circuits électroniques. Sous peine d'échauffement inacceptable de la puce, on ne sait en extraire par conduction thermique que quelques watts par centimètre carré (20 W au maximum en attachant la puce à un radiateur thermique qui est alors bien plus grand qu'elle), soit la densité de puissance de la semelle d'un fer à repasser. Un argument simple permet de montrer que la puce ne peut comporter de grands nombres de transistors fonctionnant tous en même temps : indépendamment de leur taille, les transistors délivrent un courant compris entre 0,1 et 1 mA, et nous avons vu que la tension minimale est de 1 V (et elle ne changera plus significativement). Cela signifie qu'un transistor fonctionnant continûment consomme environ de 0,1 à 1 mW. Si la puissance maximale dissipable par la puce est de 5 W/cm2, cela veut dire qu'il ne peut y avoir plus de 5 000 à 50 000 transistors opérant en continu (50 000 fois 0,1 mW = 5W, qu'il faut extraire de la puce). Ce chiffre est tout à fait représentatif des circuits actuels qui fonctionnent ainsi, réseaux de portes logiques par exemple (et ce qu'ils soient à base de transistors à effet de champ ou à base de transistors bipolaires, ces derniers étant les plus rapides mais, aussi, plus complexes à produire). Le seul gain apporté par la miniaturisation à ces circuits logiques limités en puissance dissipée est alors la faculté d'aller plus vite par transistor.

Il existe cependant des circuits intégrés de bien plus grande complexité, de quelques dizaines de millions de transistors. Cela est possible parce que ces transistors sont le plus souvent dans un état où ils ne conduisent pas de courant du tout. C'est la célèbre technologie CMOS (complementary metal oxide semiconductor) où les transistors sont associés deux à deux : l'un devant débiter du courant dans l'autre qui est « ouvert » ; il ne passe aucun courant dans des conditions stationnaires. Le courant passe seulement et uniquement lors de l'inversion de la situation logique, puisque les rôles de transistor ouvert ou fermé sont inversés : un des canaux conducteurs se remplit d'électrons alors que l'autre se vide. Si C représente la capacité du canal conducteur d'un transistor et V la tension logique (encore appelée excursion logique), alors le transistor a consommé CV2pour une opération logique, ce qui est assez représentatif de la consommation de la porte logique faite à partir de ce transistor. Pour les circuits actuels, C est de l'ordre du femtofarad (10—15 F) et V = 1 volt, d'où CV2 = 10—15 joule. La puissance maximale dissipable de 5 W/cm2 conduit alors à une densité d'opérations logiques, par centimètre carré et par seconde, de 5.1015, que l'on exprime de manière équivalente en nombre d'opérateurs logiques (les « portes ») multiplié par la fréquence d'opération : bien entendu, plus on effectue d'opérations par seconde et par porte, moins on peut utiliser de portes en même temps. C'est ainsi que l'on peut faire commuter 5 millions de portes logiques à une fréquence de 1 GHz, ou bien 500 000 à une fréquence de 10 GHz. Avec la miniaturisation, CV2 diminue grâce à C, proportionnellement à a, et la « puissance logique » par puce augmente.

Le dernier facteur limitant concerne la vitesse du circuit intégré global et est lié au temps de propagation du signal électrique sur les fils d'interconnexion. Il peut avoir deux origines. Pour les fils non optimisés, une ligne d'interconnexion est caractérisée par sa résistance R et sa capacité C (qui est bien plus grande que celle d'un seul composant à cause de la différence de taille, 1 cm au lieu d'un micromètre). Dans ce cas, le temps mis par la ligne à transmettre une information de bout en bout, c'est-à-dire pour que le changement de la tension électrique à un bout passe à l'autre bout, est égal au produit RC qui, dans les lois d'échelle pour les lignes d'interconnexion, croît malheureusement comme a2 (il a fallu, bien entendu, réduire aussi les sections des conducteurs d'interconnexions quand on a diminué les dimensions des éléments actifs d'un circuit intégré pour pouvoir commander les éléments individuellement ; R croît comme la section du fil, en a2, alors que C reste constant, la diminution d'épaisseur de l'isolant du condensateur étant compensée par la diminution de largeur). Pour tirer le meilleur parti de la miniaturisation, il faut alors utiliser des matériaux conducteurs de plus en plus performants. L'utilisation de matériaux supraconducteurs a été suggérée pour réaliser les interconnexions à longue distance sur les puces, mais ils n'ont jamais montré les propriétés espérées à température ordinaire. Le cuivre a alors été introduit vers la fin des années 1990 dans les circuits intégrés pour remplacer l'aluminium comme conducteur à longue distance. On cherche aussi à diminuer la capacité des fils conducteurs en les déposant sur un matériau isolant de très faible constante diélectrique, diminuant d'autant la capacité. Lorsque le produit RC est optimisé, la vitesse de propagation est alors limitée par la vitesse de la lumière, en tenant compte de l'indice du support de la ligne d'interconnexion : on est, dans la réalité, très proche de cette limite. Pour une vitesse de la lumière de l'ordre de 108 m/s, le temps de propagation sur une distance de 3 centimètres est de 30 picosecondes (ps), correspondant à une fréquence d'horloge de 10 GHz. On en est, en 2004, à 3 GHz dans les microprocesseurs commerciaux.

Accédez à l'intégralité de nos articles

- Des contenus variés, complets et fiables

- Accessible sur tous les écrans

- Pas de publicité

Déjà abonné ? Se connecter

Écrit par

- Claude WEISBUCH : directeur de recherche émérite au C.N.R.S., École polytechnique, Palaiseau, professeur au Materials Department de l'université de Californie à Santa Barbara

Classification

Médias

Autres références

-

AUTOMATISATION

- Écrit par Jean VAN DEN BROEK D'OBRENAN

- 11 885 mots

- 12 médias

Cette densité ne cesse de croître avec les progrès des moyens de production de lamicroélectronique. On peut ainsi disposer, sur une seule pastille de silicium, de registres de mémoire d'une capacité considérable, de sorte que des variables numériques codées en mots de 8 ou 16 bits et même 32 bits... -

CIRCUITS INTÉGRÉS

- Écrit par Frédéric PÉTROT et Franck WAJSBÜRT

- 8 998 mots

- 20 médias

Les circuits intégrés monolithiques (encore appelés puces, traduction de l'anglais chips) constituent l'approche la plus sophistiquée de la microélectronique. Leur origine technologique remonte à 1958, et leur importance économique et industrielle est devenue considérable. La miniaturisation...

-

COMMERCIALISATION DU PREMIER MICROPROCESSEUR

- Écrit par Joseph BOREL et Bruno JACOMY

- 464 mots

- 1 média

À la fin des années 1960, Marcian Hoff (surnommé Ted Hoff), un jeune ingénieur de la société américaine Intel (Integrated Electronics), propose le concept du microcalculateur (le terme microprocesseur apparaissant plus tardivement) pour répondre à une commande de la société japonaise Busicom,...

-

IMAGERIE TÉRAHERTZ

- Écrit par Bernard PIRE

- 1 427 mots

- 1 média

Le développement de sources puissantes et compactes n’a vraiment commencé qu’avec l’éclosion de lamicroélectronique et des nanotechnologies à la fin du xxe siècle. Les lasers à cascade quantique, mis au point en 1994 aux laboratoires Bell de Murray Hill (New Jersey, États-Unis) et commercialisés... - Afficher les 12 références

Voir aussi

- CODAGE

- PROGRAMME, informatique

- PIXEL

- CANAL, électronique

- CHAMP ÉLECTRIQUE

- TENSION ÉLECTRIQUE ou DIFFÉRENCE DE POTENTIEL ÉLECTRIQUE

- PUISSANCE, physique

- TRANSISTORS & THYRISTORS

- STOCKAGE D'INFORMATIONS

- CONDENSATEUR, électricité

- COURANT ÉLECTRIQUE

- DRAM (Dynamic RAM)

- CMOS (Complementary Metal Oxide Semiconductor)

- PUCE, électronique

- PUITS QUANTIQUES

- CISC (Complex Instruction Set Computer)

- RISC (Reduced Instruction Set Computer)

- PARALLÉLISME, informatique

- PIPELINE, informatique

- POTENTIEL ÉLECTRIQUE

- LIBRE PARCOURS MOYEN

- COMPOSANTS ÉLECTRONIQUES

- FIABILITÉ

- CONDUCTEURS ÉLECTRIQUES

- INSTRUCTION, informatique

- BINAIRE SYSTÈME

- ARITHMÉTIQUES OPÉRATIONS

- CIRCUITS LOGIQUES

- INFORMATION, informatique et télécommunications

- TRAJECTOIRE

- COLLISION, physique

- CHARGE ÉLECTRIQUE

- BARRIÈRE DE POTENTIEL

- ISOLANTS

- PHOTOSENSIBILITÉ, technologie

- ÉLECTRONIQUE, science et technique

- NOYCE ROBERT (1927-1990)

- NANOÉLECTRONIQUE

- INTERCONNEXIONS, électronique

- PLANAR MÉTHODE

- TENSION LOGIQUE

- ÉLECTRONS BIDIMENSIONNELS

- HORLOGE, informatique

- MÉSOSCOPIQUE ÉCHELLE

- MINIATURISATION, technologie

- ÉLECTRONS BIDIMENSIONNELS TRANSISTORS À GAZ D'

- PHOTOLITHOGRAPHIE

- IMPURETÉS, physique

- EFFET DE CHAMP TRANSISTOR À (TEC)

- GRILLE, électronique

- PUISSANCE DE CALCUL, informatique

- BOMBARDEMENT IONIQUE

- GROS SYSTÈME, informatique ou MAINFRAME

- MINI-ORDINATEUR

- COÛT

- INTÉGRATION, électronique

- DOPAGE, électronique

- NUMÉRISATION

- SIGNAL TRAITEMENT DU

- MICROPROCESSEUR

- VÉRITÉ TABLE DE

- IMAGES TRAITEMENT D'

- PERFORMANCES, technologie

- DUALITÉ ONDE-CORPUSCULE

- ARCHITECTURE, informatique

- PROCESSEUR, informatique

- OPÉRATEUR, logique

- INTEL

- TUNNEL EFFET

- SON NUMÉRIQUE

- IMAGE NUMÉRIQUE